# AUTOMATED OPTICAL INSPECTION IN CHIP MANUFACTURING

### PUBLIC

Florian Kälber, Frank Karstens **BASLER** SEPTEMBER 2022

#### SECURE CONNECTIONS FOR A SMARTER WORLD

PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

### AGENDA

The Problem

Proof of concept

Prototype

Live Demo

# The Problem

#### PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

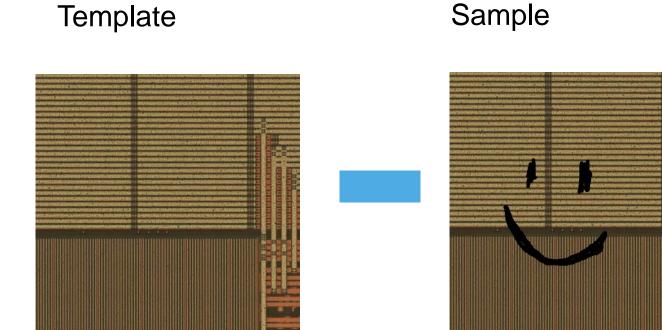

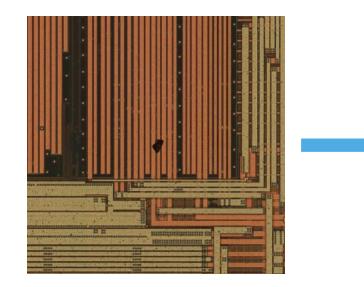

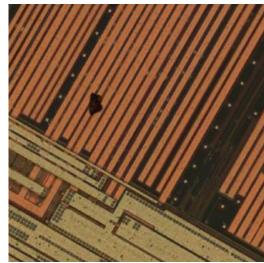

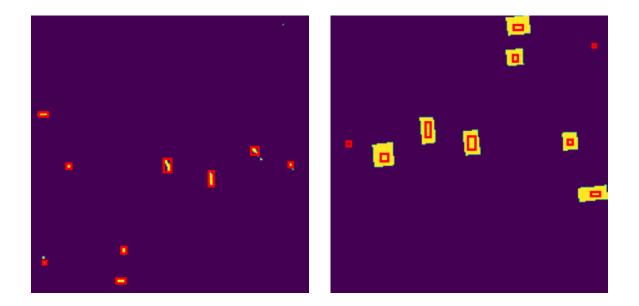

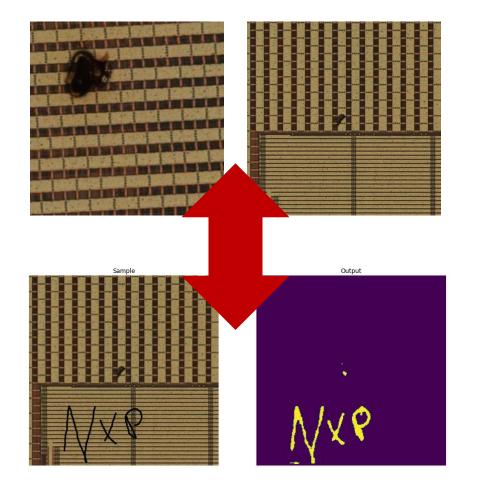

#### **TRADITIONAL WAVER DEFECT DETECTION METHODS**

Templates available: isolate defects Idea: use difference as labels for supervised learning?

Sample

#### **Difference**/ label

# Proof of concept

#### PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

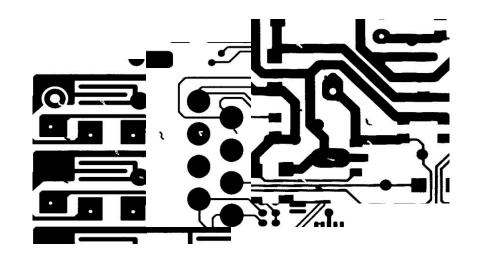

#### DATASETS

#### Public Deep PCB Dataset

- 1500 grayscale samples

- Templates available

- 3-12 defects per sample

- Bounding box annotations

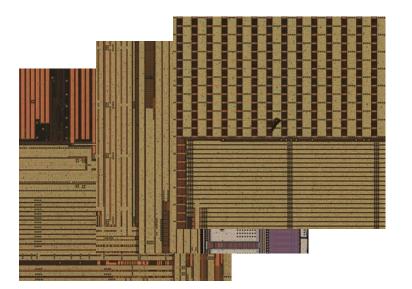

### Internal NXP Chip defect Dataset

- 1474 color samples

- Templates available

- 1 centered defect per sample

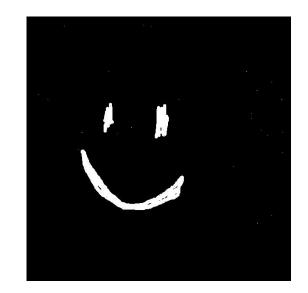

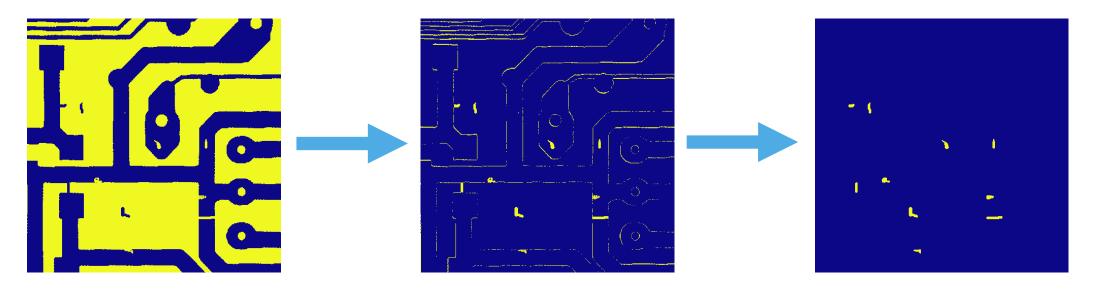

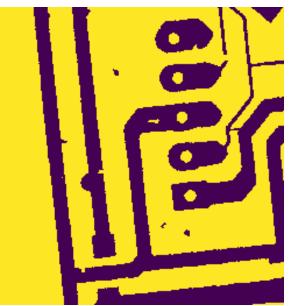

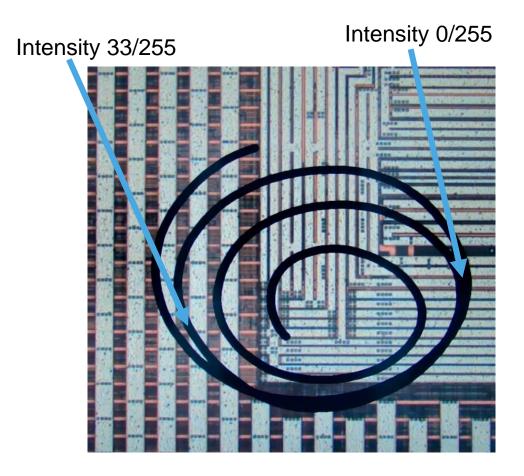

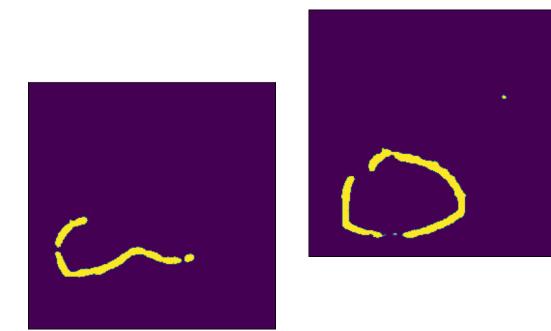

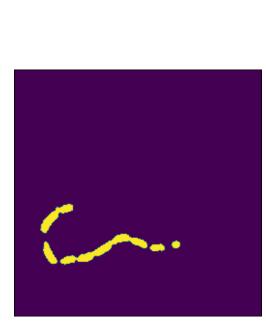

#### **PREPROCESSING – LABEL GENERATION**

Pipeline:

- Image registration (≈ align images)

- Defect isolation

- Binarization (chip defect dataset)

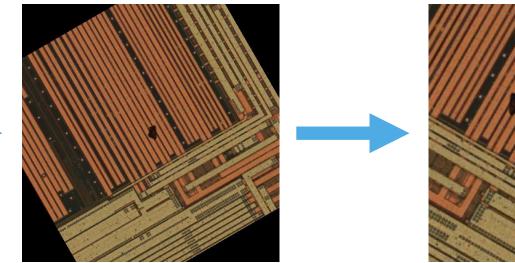

#### **PREPROCESSING – DATA AUGMENTATION**

*increase the amount of data by adding slightly modified copies of already existing data or newly created synthetic data from existing data* Augmentation transformations:

- Rotation

- Cropping

- Horizontal & vertical flipping

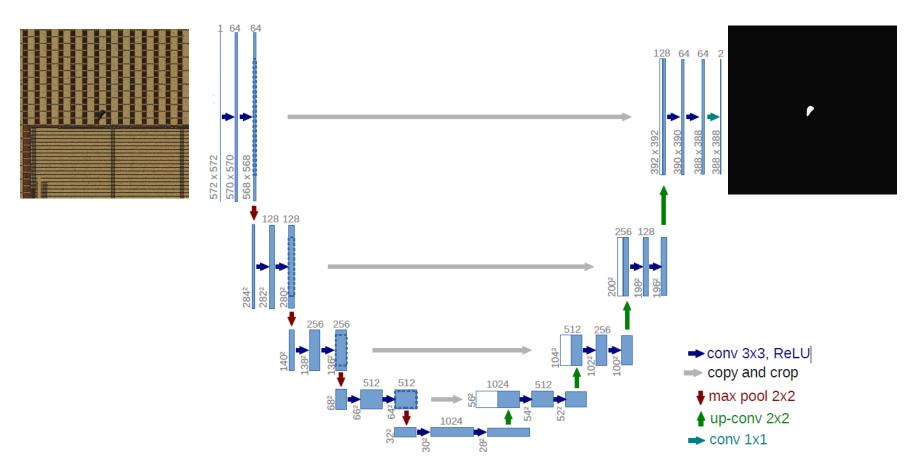

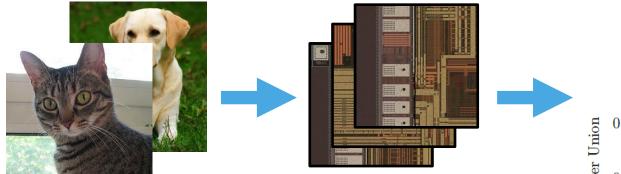

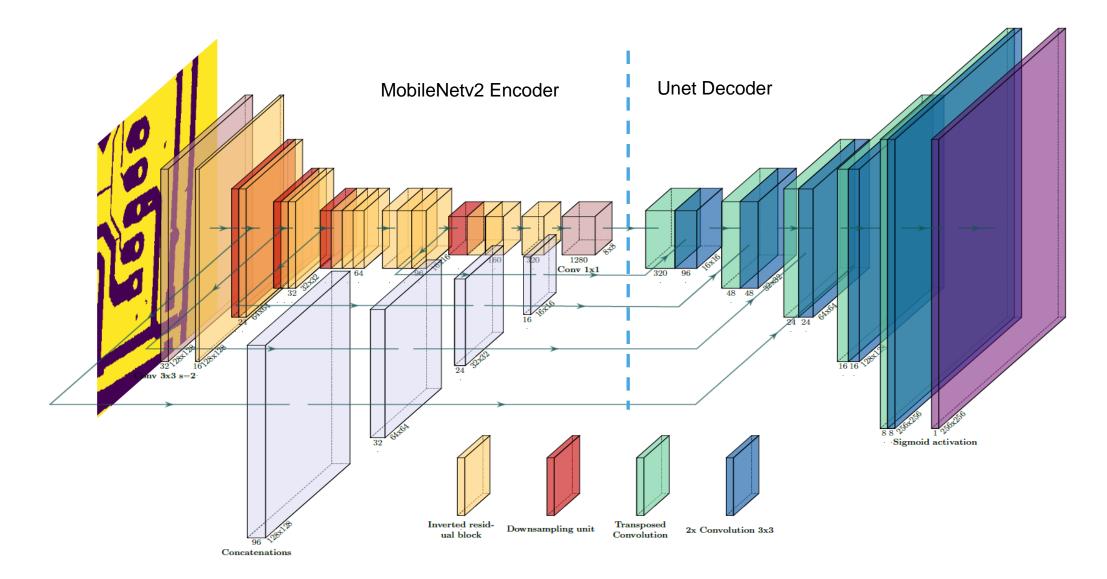

#### UNET: FULLY CONVOLUTIONAL IMAGE SEGMENTATION MODEL

Source: U-Net: Convolutional Networks for Biomedical Image Segmentation, Ronneberger et al. 2015

#### OUTPUTS

0

1

-

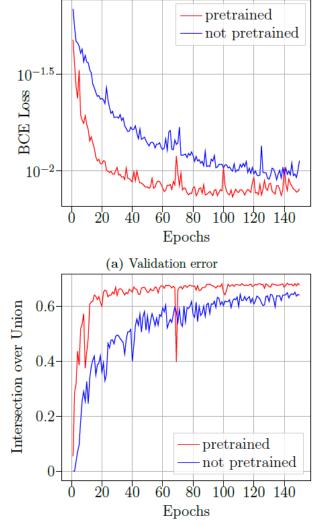

#### PRETRAINING

• Using pretrained weights (ImageNet) improves results

#### SHUFFELNET & MOBILENET ENCODER

NP

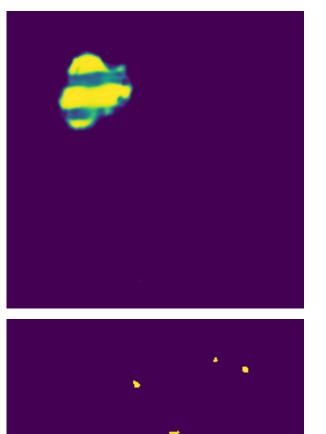

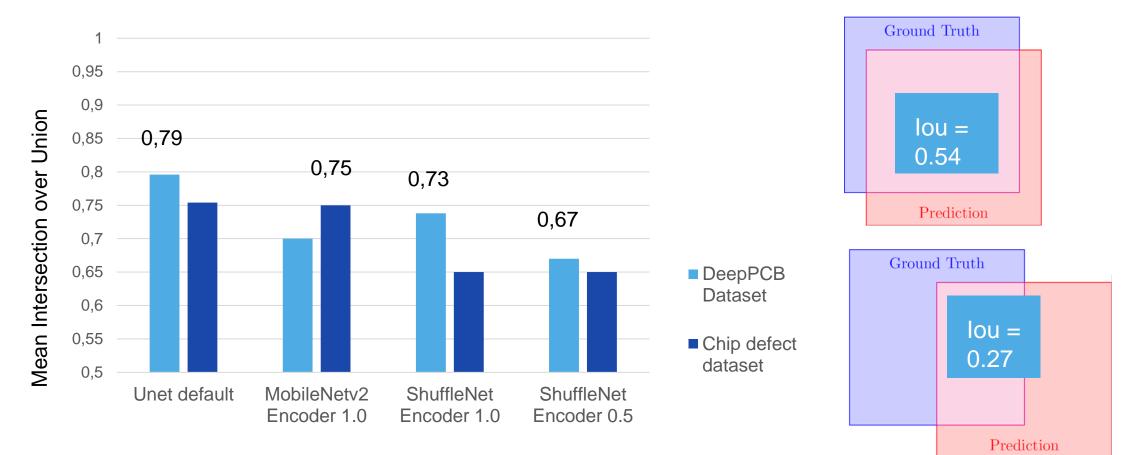

#### **RESULTS/ EVALUATION**

### Intersection over Union:

$\frac{Ground \ Truth \cap Prediction}{Ground \ Truth \cup Prediction}$

#### DEFECT DETECTION

- OpenPCB Dataset

- Number of defects in Testset: 19610

|           | Shuffle<br>Unet 0.5 | MobileUnet<br>v2 1.0 |

|-----------|---------------------|----------------------|

| TP        | 19040               | 18919                |

| FP        | 1770                | 718                  |

| FN        | 570                 | 718                  |

| Precision | 0,915               | 0,964                |

#### **DBScan Clustering:**

#### **COMPUTATIONAL PERFORMANCE**

|           |         | UNet    |     | MobileUNetv2 1.0 |         | ShuffleUNet 0.5 |         |         |       |

|-----------|---------|---------|-----|------------------|---------|-----------------|---------|---------|-------|

|           | Encoder | Decoder | Σ   | Encoder          | Decoder | Σ               | Encoder | Decoder | Σ     |

| Parameter | 19M     | 12M     | 31M | 2,2M             | 2,2M    | 4,4M            | 0,34M   | 1,2M    | 1,6M  |

| FLOPs     | 13G     | 24G     | 37G | 0.32G            | 0.43G   | 0.75G           | 0.04G   | 0.56G   | 0.61G |

#### **PROOF OF CONCEPT - CONCLUSION**

- Good Image segmentation results, as well as classification:

- IoU: ≈0,7

- Precision: ≥0,96

- Model small enough for embedded applications

- Complement traditional defect detection with a more flexibel system (react to changes in manicaturing, inbetween steps of an assembly line,..)

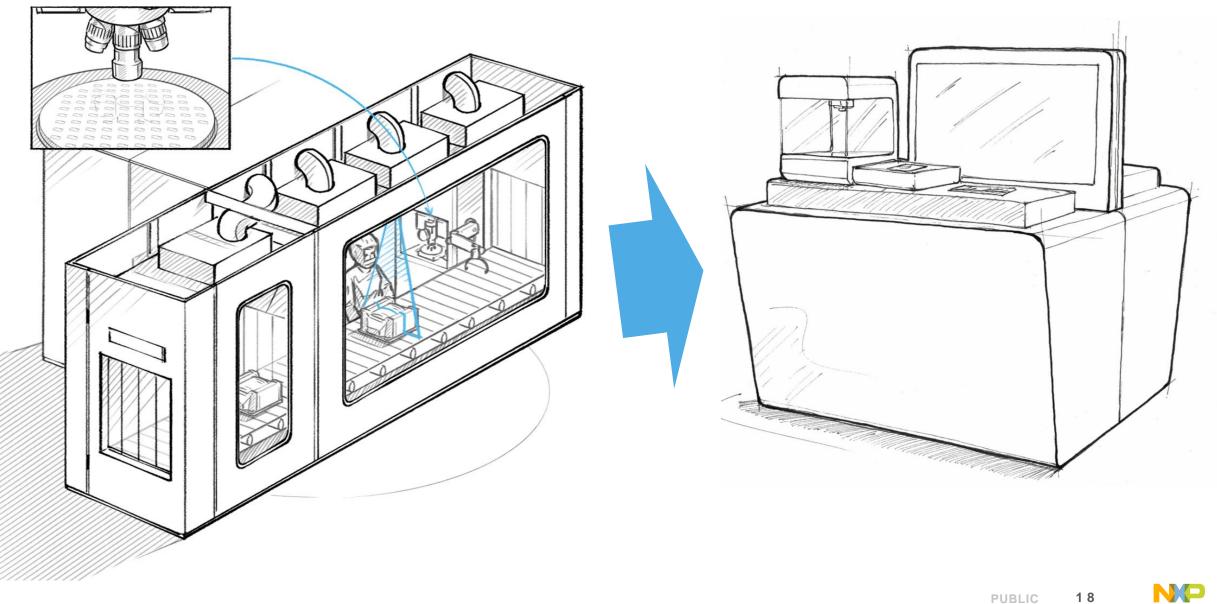

# Prototype

#### PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

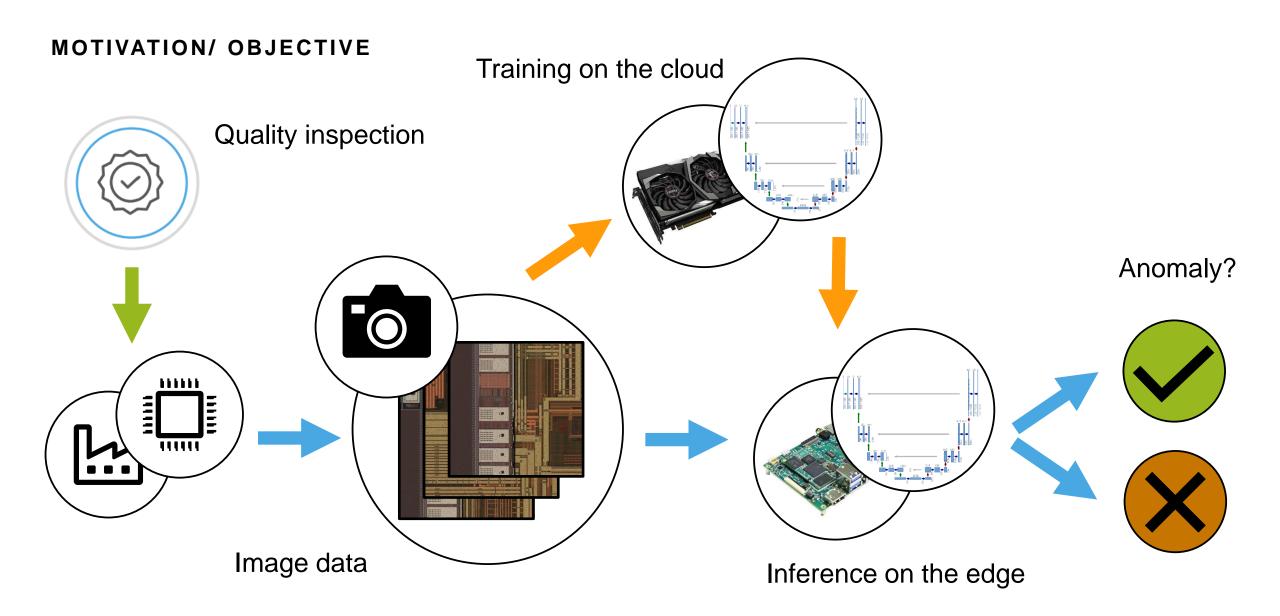

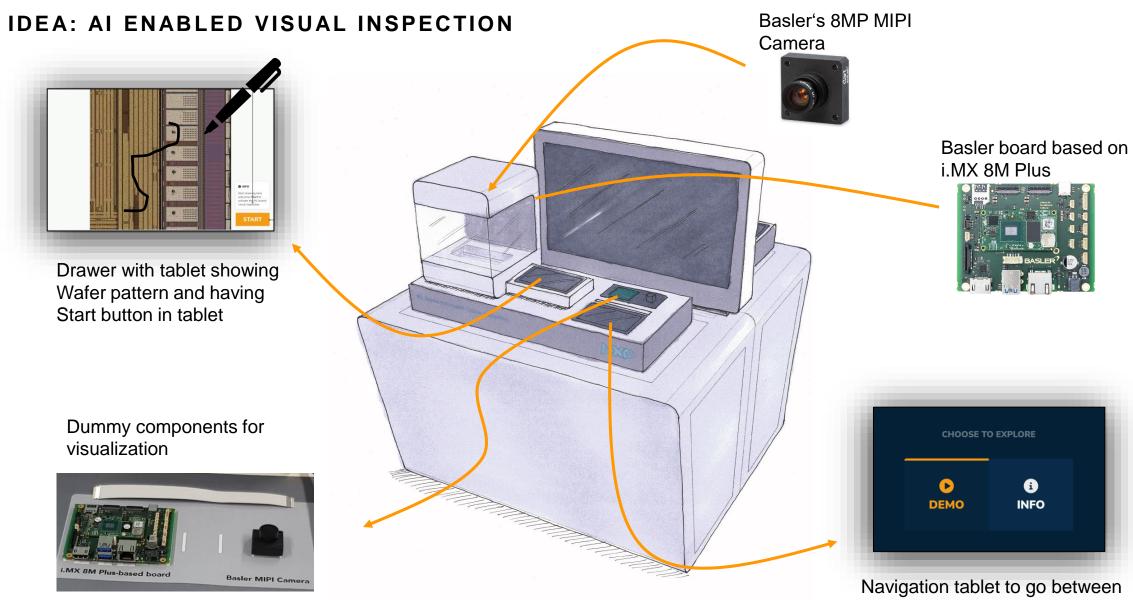

#### IDEA: AI ENABLED VISUAL INSPECTION

Demo and Info mode

#### **MODEL RETRAINING – DATA CHALLENGE**

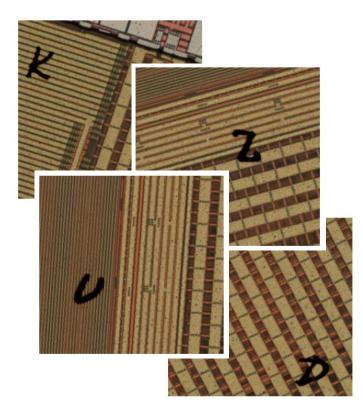

Manufacturing related defects vs artificial anomalies

"Photo of Photo on Display"

#### **MODEL RETRAINING – DATA CHALLENGE**

#### Two possibilities:

Utilizes Preprocessing/semisynthetic data to mimic final input

- + no new training data necessary

- Performance suffers

Generate new Training set similar to final input data

- + best performance

- Tedious image registration/train set generation (automation process necessary)

- intensity and contrast noise on train samples

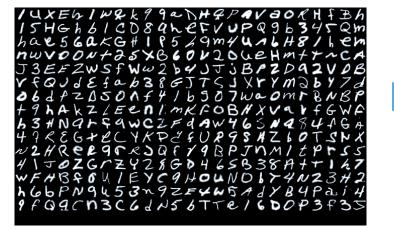

- EMNIST Dataset:

- Handwritten letters as "Anomalies"

- 70,000 images 28x28 pixels

#### MODEL QUANTIZATION/ PERFORMANCE

- 32bit, converted from PyTorch to Onnx

- Running on ARM cores

- ARM NN Library

- ≈ 240ms Inference time

- Fully quantized 8bit TensorFlow Lite model

- Running completely on Neural Processing Unit

- ≈ 9,5ms Inference time

22

PUBLIC

# NXP / Basler Wafer Inspection Demo

### @ Embedded world 2022

Public | © Basler AG

## **Hardware Wafer Inspection Demo**

### Basler Embedded Vision Processing Kit

- Development Kit for Vision Applications

- Suitable also for series production (population options to reduce unit costs)

- Complete interface population:

- 2x MIPI-CSI 2, 2x USB 3.0, GigE, HDMI, GPIOs, I2C, SPI, LVDS, UART, CAN, USB 2.0, M 2.0, Bluetooth, Wi-Fi

- Equipped with NXP i.MX8M Plus SoC

## **Hardware Wafer Inspection Demo**

### NXP i.MX8M Plus Featureset

- Neural Processing Unit (NPU) with up to 2.3 TOPS

- Up to 2 cameras with MIPI CSI-2 interface, 1080p60 stereo vision

- Image Signal Processor (ISP) for 4K vision, HDR, de-warp (e.g. fish-eye lens correction)

- High resolution video compression including video encode (including h.265) and decode

- 3D and 2D graphics acceleration GPU based

- Real-time processing with Cortex-M7 @800MHz

- 4x CortexA53 @1.8GHz

- 14nm FinFet, low power, high performance

- Robust control networks supported by dual CAN FD and dual Gigabit Ethernet with Time Sensitive Networking (TSN)

# BASLER

| Security           | Main CPU Platform                             | Display                                                           |  |  |

|--------------------|-----------------------------------------------|-------------------------------------------------------------------|--|--|

| Arm®TrustZone ®    |                                               | HDMI 2.0a Tx (eARC) with PHY                                      |  |  |

| Aminimusizone      | 4 x Arm <sup>®</sup> Cortex <sup>®</sup> -A53 | MIPI-DSI (4-lane) with PHY                                        |  |  |

| DRM Ciphers        |                                               | 1 x LVDS Tx (4 or 8-lane) with PHY                                |  |  |

|                    | 32 KB I-cache 32 KB D-cache                   | Audio                                                             |  |  |

| Secure Clock       | Arm NEON™ FPU                                 | 18 x I2S TDM 32 bit at 768 kHz                                    |  |  |

| eFuse Key Storage  | 512 KB L2 Cache (ECC)                         | SP/DIF Tx and Rx                                                  |  |  |

| , ,                | Secondary Cores                               | eARC (HDMI)                                                       |  |  |

| Random Number      | Tensilica <sup>®</sup> HiFi 4 DSP Cortex-M7   | ASRC                                                              |  |  |

| 32 KB Secure RAM   | 768 KB On-chip RAM (ECC)                      | 8-ch. PDM Microphone Input                                        |  |  |

|                    |                                               | Connectivity and I/O                                              |  |  |

| System Control     | Machine Learning                              | 2 x USB 3.0/2.0 OTG with PHY                                      |  |  |

| Smart DMA x3       | Machine Learning Accelerator: 2.25 TOPS       | 2 x Gbit Ethernet with IEEE ®1588, AVB<br>(One also supports TSN) |  |  |

| XTAL               | Graphics<br>3D Graphics: GC7000UL             | 2 x CAN FD                                                        |  |  |

| PLLs               | 2D Graphics: GC520L                           | 1 x PCle ®Gen 3 – 1-lane<br>L1 Substates                          |  |  |

| Watchdog x 3       | Video                                         | 4 x UART 5 Mbit/s 5 x I <sup>2</sup> C, 3 x SPI                   |  |  |

| PWM x 4            | 1080p60 H.265, H.264, VP9, VP8 decoder        | External Memory                                                   |  |  |

| Timer x 6          | 1080p60 H.265, H.264 encoder                  | x16/x32 LPDDR4/DDR4/DDR3L<br>(Inline ECC)                         |  |  |

| Secure JTAG        | 10.1                                          | 3 x SDIO3.0/MMC5.1                                                |  |  |

| Secure JIAG        | Vision                                        | Dual-ch. QuadSPI (XIP) or                                         |  |  |

| Temperature Sensor | Camera ISP (2 x 187 MP/1 x 375 MP) dewarp     | 1 x OctaISPI (XIP)                                                |  |  |

|                    | 2 x MIPI-CSI (4-lane) with PHY                | NAND Controller (BCH62)                                           |  |  |

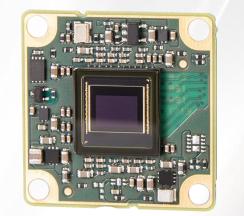

## **Hardware Wafer Inspection Demo**

### Basler dart MIPI CSI-2 camera module

- 8 MPix, 30 fps

- MIPI CSI-2 interface

- Uses NXP i.MX8M Plus Image Signal Processor (ISP)

- GenICam compliant compatible to Basler camera SDK (pylon) or gstreamer

- Wide angle lens using the i.MX8M Plus Dewarping hardware block

# BASLER

### SECURE CONNECTIONS FOR A SMARTER WORLD

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.